碩士學位 請求論文

3전극 면방전 플라즈마 디스플레이의

교류 구동특성에 關한 研究

慶州大學校大學院

컴퓨터電子工學科

孫 賢 聖

指導教授 廉 正 德

2005年 2月

016765

3전극 면방전 플라즈마 디스플레이의

교류 구동특성에 關한 研究

慶州大學校 大學院

컴퓨터電子工學科

孫 賢 聖

이 論文을 碩士學位 論文으로 提出함

指導教授 廉 正 德

2005年 2月

孫賢聖의 碩士學位論文을 認准함

審查委員 乞德煥

審查委員 廉正德

審查委員 金基洙

慶州大學校大學院

2005年 2月

## [ 목 차 ]

|                                  |    |

|----------------------------------|----|

| I. 서론 .....                      | 1  |

| II. PDP의 구조 및 구동원리 .....         | 3  |

| 1. 일반적인 PDP 구동법 .....            | 4  |

| 2. 3전극 면방전 AC PDP의 구조 .....      | 5  |

| 3. 3전극 면방전 AC PDP의 구동원리 .....    | 7  |

| 4. PDP의 화상구현 원리 .....            | 10 |

| III. PDP 구동 실험장치의 개발 .....       | 11 |

| 1. 펄스 발생부 .....                  | 12 |

| 2. 구동 회로부 .....                  | 13 |

| 3. PDP 구동을 위한 타이밍 펄스의 설계 .....   | 14 |

| 4. 측정장비 .....                    | 18 |

| IV. PDP의 교류구동 특성 및 평가 .....      | 19 |

| 1. 초기화기간의 방전특성 .....             | 21 |

| 2. 각 구동 펄스의 동작 마진정의 및 특성평가 ..... | 23 |

| 3. 구현된 화상 .....                  | 29 |

| V. 결론 .....                      | 31 |

| [참고문헌] .....                     | 33 |

| [연구실적] .....                     | 34 |

| [Abstract] .....                 | 35 |

## [ 그림목차 ]

|                                                           |    |

|-----------------------------------------------------------|----|

| 그림 1. PDP의 구조 .....                                       | 3  |

| 그림 2. PDP 구동방식 .....                                      | 5  |

| 그림 3. 3전극 면방전 AC PDP의 구조와 발광원리.....                       | 6  |

| 그림 4. ADS 구동방식의 타이밍도.....                                 | 9  |

| 그림 5. ADS 구동법에 의한 방전 제어과정.....                            | 9  |

| 그림 6. PDP의 계조구현 원리도 .....                                 | 10 |

| 그림 7. PDP 구동실험 장치의 구성도와 실제사진 .....                        | 12 |

| 그림 8. PLD를 사용한 타이밍 펄스 발생부 .....                           | 13 |

| 그림 9. 고전압 스위칭 회로부.....                                    | 14 |

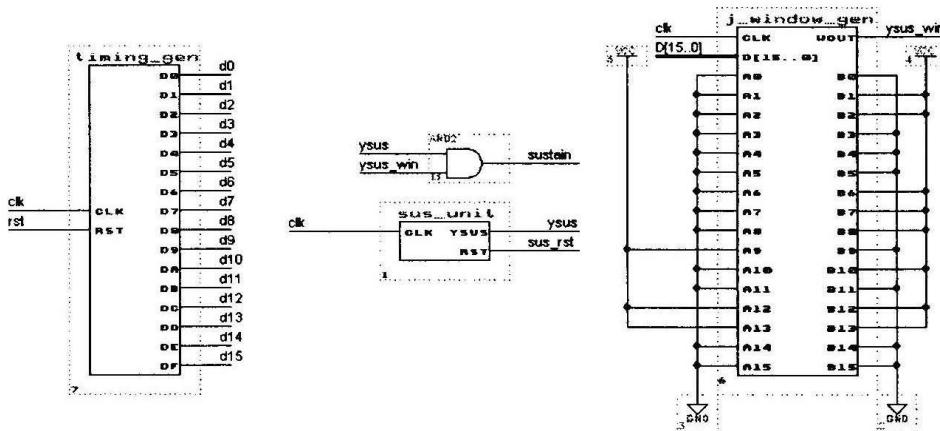

| 그림 10. Timing generator 블록과 시뮬레이션 출력값.....                | 15 |

| 그림 11. Pulse generator와 Window generator의 블록도.....        | 16 |

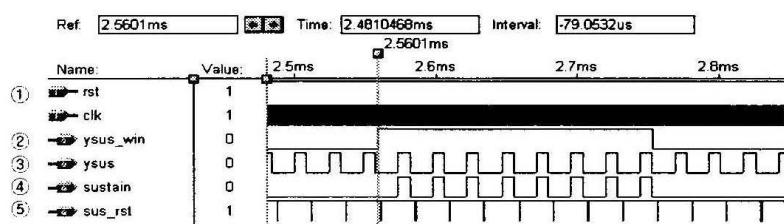

| 그림 12. Pulse generator와 Window generator의 블록의 시뮬레이션 ..... | 17 |

| 그림 13. Sustain 펄스를 설계한 블록도 .....                          | 17 |

| 그림 14. Sustain 블록의 출력 시뮬레이션 .....                         | 17 |

| 그림 15. PDP 측정장비 .....                                     | 18 |

| 그림 16. 실제실험에 사용한 3전극 AC PDP .....                         | 19 |

| 그림 17. 실제 실험에 사용한 sub-field의 구조.....                      | 20 |

| 그림 18. 휙도의 측정 방법 .....                                    | 20 |

| 그림 19. Sub-field의 표시방전 유지펄스의 개수에 따른 휙도 .....              | 21 |

| 그림 20. 램프펄스에 의한 광출력 .....                                 | 22 |

| 그림 21. 자기소거방전 .....                                       | 23 |

| 그림 22. 표시방전 유지펄스 전압에 따른 방전의 변화.....                       | 24 |

| 그림 23. 표시방전유지 펄스폭 변화에 따른 전압 마진과 평균휘도 .....                | 25 |

| 그림 24. 어드레스 펄스 전압에 따른 방전의 변화.....                         | 27 |

| 그림 25. 어드레스 펄스폭 변화에 따른 전압마진과 휙도의 측정 .....                 | 27 |

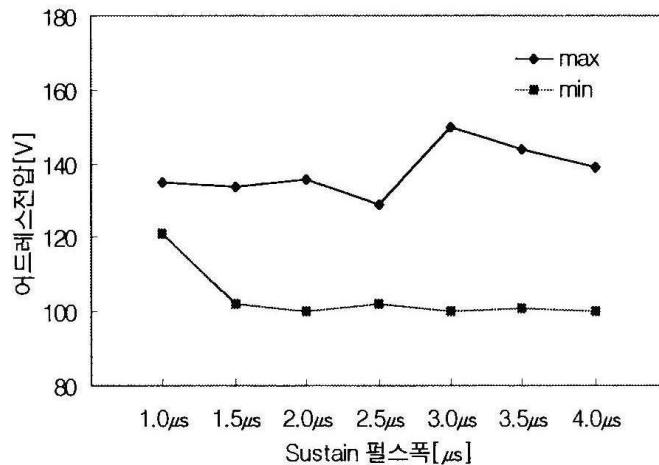

| 그림 26. 표시방전유지 펄스폭에 의한 어드레스 동작마진 .....                     | 28 |

| 그림 27. 16계조 구현.....                                       | 30 |

| 그림 28. 화상 구현.....                                         | 30 |

| 표 1. 어드레스 펄스폭과 sub-field의 개수에 따른 표시방전 유지펄스<br>의 수.....    | 29 |

## I. 서론

현대 사회는 디지털기반의 정보화 사회이다. 따라서 정보획득의 수단이 매우 중요하다고 할 수 있다. 디스플레이 장치는 시각적 정보전달 수단으로써 많은 정보를 보다 쉽게 전달하기 위해 연구 개발되어 왔다. 대표적 디스플레이인 브라운관(CRT: Cathode Ray Tube)은 현재까지 가장 널리 보급되어진 디스플레이 소자이다. 그러나 화면의 크기에 비례하여 장치의 크기와 무게 등이 증가되는 단점으로 대화면화의 한계성을 가진다. 때문에 디스플레이장치 개발업자들은 액정 디스플레이소자(LCD: Liquid Crystal Display), 전계발광 디스플레이소자(ELD: Electro Luminescent Display) 그리고 플라즈마 디스플레이패널(PDP: Plasma Display Panel)과 같은 평판 디스플레이로 점차 눈을 돌리기 시작하였다. 현재는 가정용 TV, PC용 모니터, 극장이나 역의 대형 광고모니터 등 평판 디스플레이장치로 대체된 상품들을 주위에서 쉽게 찾아 볼 수 있다.

그 중에서도 플라즈마 디스플레이 패널은 빠른 응답특성, 넓은 광 시야각, 간단한 구조로 대화면화가 용이하고 뛰어난 화질을 갖는 자발광 소자이다. 또한 디지털신호로 휘도를 제어하므로 디지털 TV에 가장 적합한 디스플레이 소자라고 할 수 있다.[1][2]

PDP는 1966년 미국 일리노이 대학의 Bitger와 Slottow에 의해 최초로 발표되었다. 이 PDP는 현재 AC 방식으로 분류되어지며 DC 방식은 1968년 네덜란드 필립스사의 Bohr가 발표하였다.[3] PDP의 AC형 면방전 구조는 1990년 일본 후지쯔(Fujitsu)사에 의해 개발되었으며, 또한 동사는 ADS(Address Display Separate)구동기술을 개발하여 1992년 세계 최초로 21인치 VGA급 PDP를 발표, 1993년에는 21인치 컬러 AC PDP의 양산을 시작하였다.[4][5] 이후 3전극 면방전 패널 구조와 ADS 구동기술은 거의 모든 PDP의 상품화에 적용되어 왔으며 현재는 그와 같은 패널구조와 구동방법을 일반적으로 사용하고 있다.[6] 그러므로 우리가 PDP 분야에서 선진국 대비 우위의 경쟁력을 확보하게 위해서는 ADS 구동기술과 같은 PDP 표준 기술을 대체하는 신 구동기술의 개발이 절실히 필요하다.

이와 같은 구동기술을 연구하고 개발하기 위해서는 구동파형을 쉽게 설계하고 변경할 수 있어야 한다. 따라서 본 연구에서는 PLD(Programmable

Logic Device)를 사용하여 개인용 컴퓨터상에서 쉽게 파형을 설계하고 시뮬레이션 하며, 그 결과 생성된 펄스들로 고전압 펄스 출력을 얻을 수 있는 PDP용 구동실험 장치를 개발하였다. 또한 이 실험 장치를 이용하여 상용화 된 3전극 면방전 AC PDP에 ADS 구동법을 적용하여 동화상을 구현하였으며 초기화, 어드레스, 그리고 표시방전유지 기간을 구성하는 각 구동펄스들의 관계에 대한 실험적인 해석 및 휘도특성을 알아보았다.

## II. PDP의 구조 및 구동원리

PDP는 방전현상을 이용한 디스플레이로 정의된다. 여기서 방전현상이란 전계에 의해 가속된 하전입자를 다른 중성원자나 분자에 충돌시켜 그 원자나 분자를 전리시키는 기체방전현상을 뜻한다.[7] PDP의 각 셀들은 미세한 크기의 방전램프에 비유할 수 있으며 전압인가 유무에 따라 방전공간이 ON/OFF되는 bi-stable 모드를 가진다. PDP는 이러한 방전램프들의 집합체이며 각각의 램프들을 ON/OFF 하여 패널 면에 화상을 표시하는 디스플레이 소자이다.

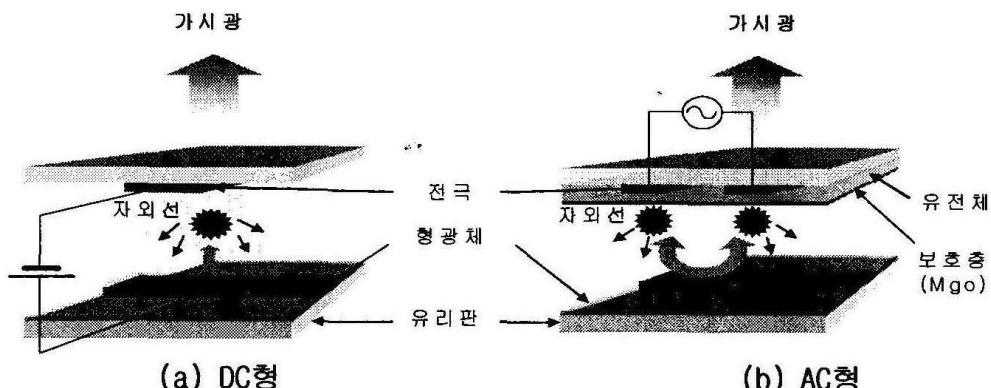

PDP의 구조는 전압인가 방법에 따라 고주파 방전현상을 이용하는 AC형과 음글로우(negative glow)의 직류방전을 이용하는 DC형으로 나누어진다. 그림 1은 DC형과 AC형의 PDP 구조를 비교하여 나타낸 그림이다. DC형의 구조인 그림 1(a)는 상하의 유리판에 직교하는 두 전극을 설치하여 이 두 전극사이에서 방전을 발생시키는 대향방전구조를 사용한다. DC형은 설치된 전극들이 방전공간에 노출되어 있어서 방전시 양이온이 음극에 충돌하는 스퍼터링(Sputtering)현상에 의한 전극손상으로 수명이 짧으나 잡광이 없어 화질이 좋은 장점이 있다. 그림 1(b)는 AC형의 구조를 나타낸 것으로 DC형과는 달리 전극이 유전층으로 덮여있다. 한쪽유리판에는 평행한 두 전극이 설치되어 있으며 다른 한쪽 유리판에는 평행전극과 직교하는 전극이 있어서 평행전극 간 방전을 이용하는 면방전구조와 대향방전구조를 모두 사용한다. AC형은 전극이 방전과 분리되어 있어 수명이 길지만 잡광에 의한 화질저하의 단점이 있다.[3]

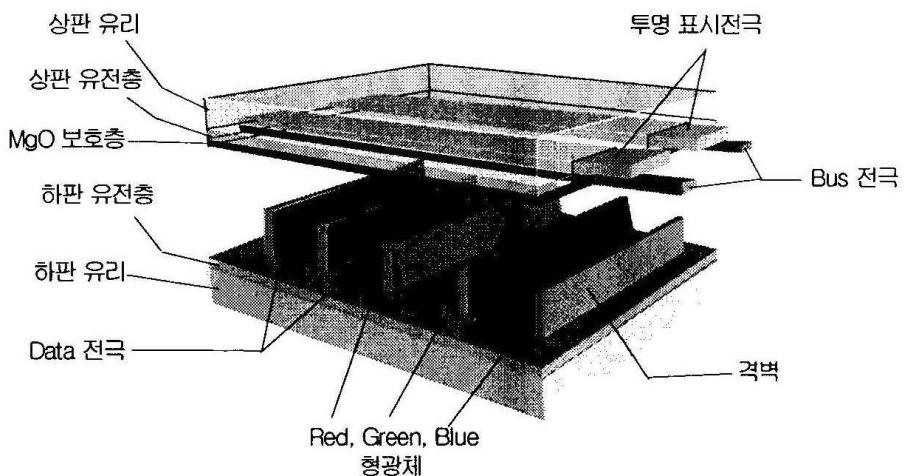

그림 1. PDP의 구조

Fig. 1. The structure of PDP

## 1. 일반적인 PDP 구동법

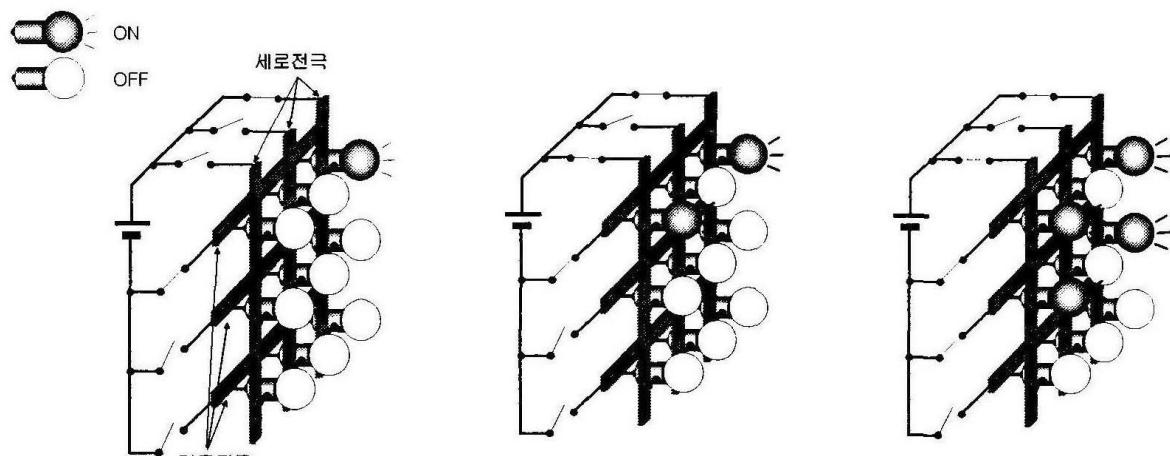

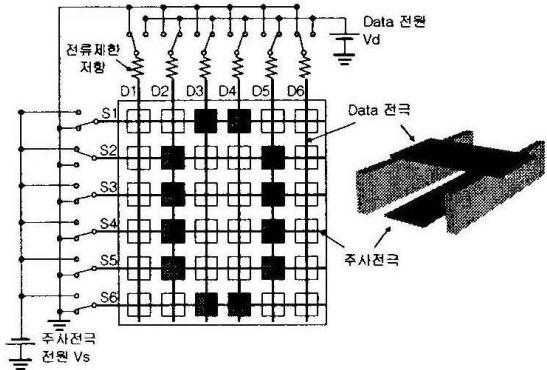

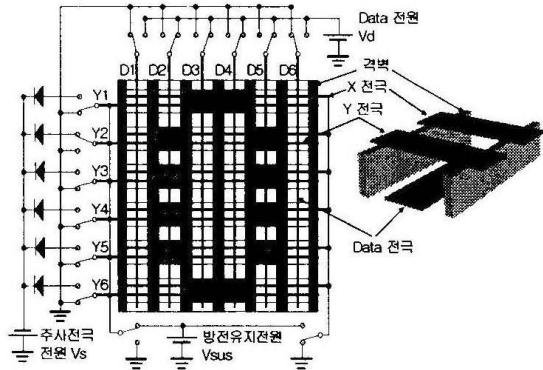

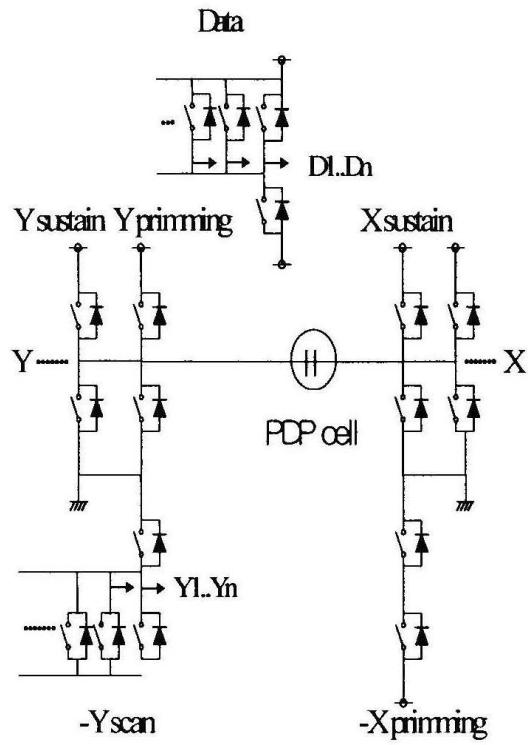

PDP는 일반적으로 Matrix 구동방식을 사용한다. 이 구동방식은 같은 전극상의 각 셀들을 선택적으로 방전시킬 수 있으므로 구동회로 소자의 수를 줄일 수 있는 장점이 있다. 예들 들어 가로 10개, 세로 10개의 전극을 교차하여 배열하면 이 20개의 전극만으로 100개의 셀을 구동할 수 있다. 그럼 2(a)는 Matrix 구동방식의 원리도를 나타낸 것이다. 그림에서 볼 수 있듯이 가로 전극과 세로 전극의 스위치가 모두 ON이 된 경우에만 전구에 불이 켜진다. 그럼 2(b)와 2(c)는 PDP 구동방식에서 각각 2전극 대향방전구조와 3전극 면방전구조를 나타낸 그림이다. DC형은 모두 그림 2(b)의 대향방전구조를 사용한다. 대향방전구조의 Data전극에는 방전 전류를 제한하기 위한 저항이 설치되어 있다. 주사전극은 위에서 아래의 방향으로 순차적으로 전압이 인가되어지며 Data전극과 동시에 전압이 인가된 경우에만 표시 방전이 발생된다. 이 방전방식은 주사전극의 개수에 비례하여 휘도가 저하되는 단점이 있다. 그럼 2(c)는 3전극 면방전구조로 대향방전구조와 마찬가지로 Data전극과 주사전극에 동시에 전압이 인가될 경우 방전이 발생된다. 이때의 방전은 표시 방전을 위한 셀 선택 방전이며, 셀 선택 방전이후 X와 Y의 표시 전극에 방전유지전압을 교대로 인가하여 표시방전을 유지시킨다. 이 방전방식은 벽전하에 의한 Memory 효과를 이용하므로 DC형에 비해 휘도가 높다.

(a) Matrix 구동방식의 원리

(b) 2전극 대향방전구조

(c) 3전극 면방전구조

그림 2. PDP 구동방식

Fig. 2. The driving method for PDP

## 2. 3전극 면방전 AC PDP의 구조

그림 3(a)는 3전극 면방전 AC PDP의 구조를 나타낸 그림이다. 이 구조는 휘도와 발광효율을 크게 개선시켜[4] 1990년대 등장한 이후로 현재까지 가장 널리 사용되는 패널구조이다.

상판유리와 하판유리는 약  $100 \sim 150\mu\text{m}$ 의 간격으로 떨어져 있으며 방전 공간 내부에는 불활성 가스인 Buffer가스(He, Ne, Ar, Kr)와 Source가스(Xe)가 혼합되어 채워져 있다. 일반적으로 Ne-Xe의 혼합가스를 사용하여 Xe가스의 방전시 발생되는 진공자외선을 이용하여 형광체를 여기 시킨다. X, Y의 표시전극은 상판유리에 위치하며 빛이 투과할 수 있는 투명 전도성 물질인 ITO(Indium Tin Oxide)로 제작 되어있다. 이 투명 표시전극에는 패널의 대형화에 따라 길어진 전극의 저항성분을 줄이기 위해 미세한 금속의 버스 전극이 형성되어 있다. 이 전극들은 다시 투명 유전층과 스퍼터링을 방지하기 위한 산화마그네슘(MgO) 보호층으로 덮여져 있다. 또한 MgO 보호층은 효율적인 방전 발생을 위한 2차전자방출의 기능도 한다. 하판유리에는 셀을 선택하기 위한 Data전극이 설치되어있으며 전극 위로 유전층이 덮여있다. 이 유전층위에는 인접 셀에서 발생된 방전영향에 의한 크로스 톡(Cross talk) 현상을 방지하기 위한 목적으로 표시전극과 수직으로 격벽이 형성되어 있다. 각 격벽사이의 공간이 하나의 셀을 구성하며 각 셀은 Red, Green, Blue의 형광체가 도포되어 있다. 그림 3(b)는 PDP의 발광원리를

나타낸 그림이다. PDP 각 셀에 위치한 전극들 사이에 외부전계가 인가되면 방전공간내부에서는 가스방전이 발생되며 이 때 147nm의 파장을 갖는 진공 자외선(VUV: Vacuum Ultra Violet)이 생성된다. 이 진공자외선은 격벽 내부에 도포되어 있는 형광체를 발광시키며, 각 형광체에 따라 발생된 R, G, B의 가시광이 상판의 투명전극을 통하여 우리 눈에 보여 지게 되는 것이다.[3]

(a) 3전극 면방전 AC PDP의 구조

(b) 발광원리

그림 3. 3전극 면방전 AC PDP의 구조와 발광원리

Fig. 3. The structure of 3 electrodes surface discharge AC PDP and the radiation principle of PDP cell

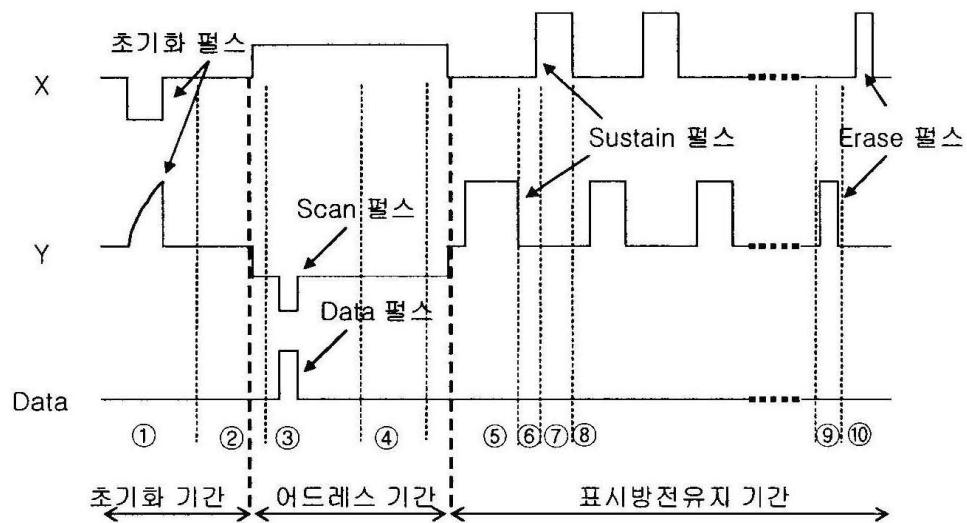

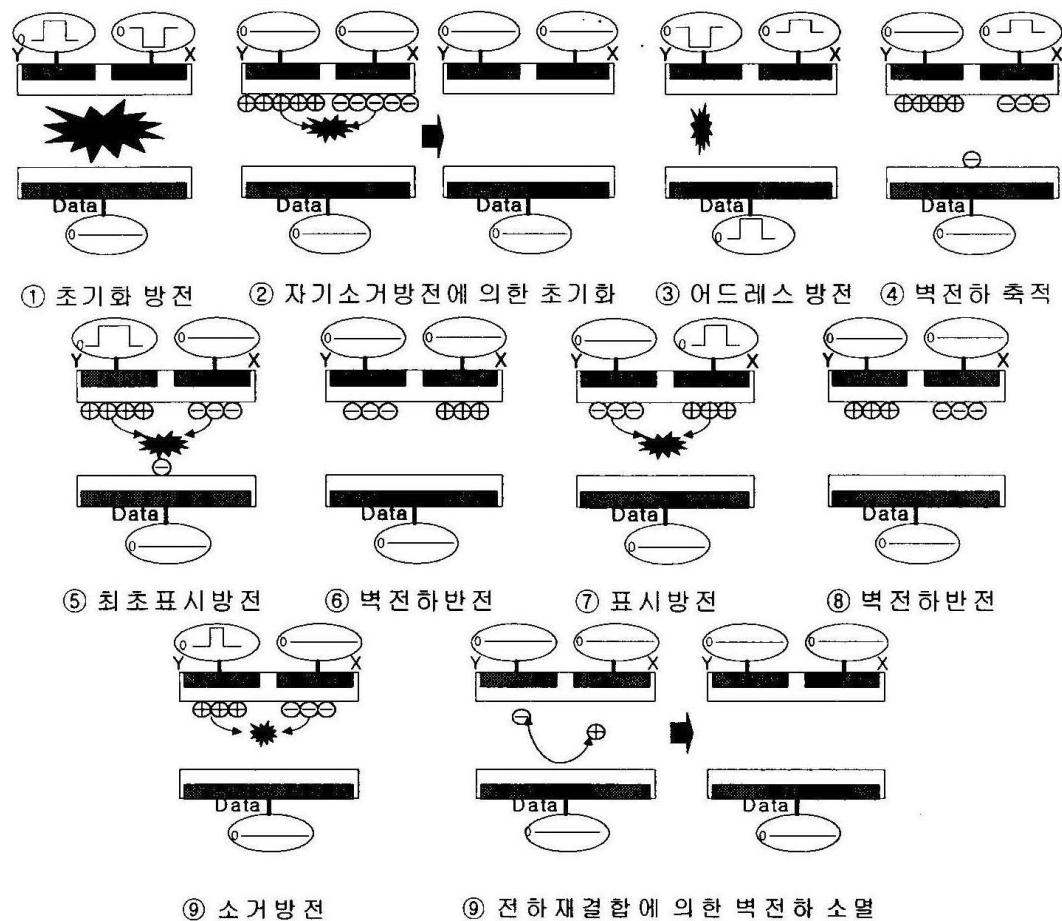

### 3. 3전극 면방전 AC PDP의 구동원리

PDP 내부의 각 방전공간은 전극간 전압이 인가되더라도 방전개시 전압 이하의 인가전압에서는 방전이 일어나지 않는 강한 비선형성을 가지므로 이러한 성질을 이용하면 벽전하에 의한 Memory 효과로 디지털 방식의 계조구현을 할 수 있다. 현재 연구되고 있는 PDP의 구동방식은 ADS 구동방식, AWD(Address While Display)구동방식, DC형을 위한 Pulse memory 구동방식이 있으나 본 논문에서는 현재 가장 널리 사용되고 있는 3전극 면방전 구조의 대표적인 구동방식인 ADS 구동방식만을 다룬다. 그림 4는 ADS 구동법의 일반적인 타이밍도이다. ADS 구동방식은 1 TV-field의 한 정된 시간을 다수의 서브필드(SF: Sub-Field)로 나누고, 각 SF는 다시 초기화(Reset), 어드레스(Address), 표시방전유지(Sustain) 기간으로 나누어 진다. 그림 5는 그림 4의 ADS 구동타이밍의 각 기간에 대응되는 방전 메커니즘이다.

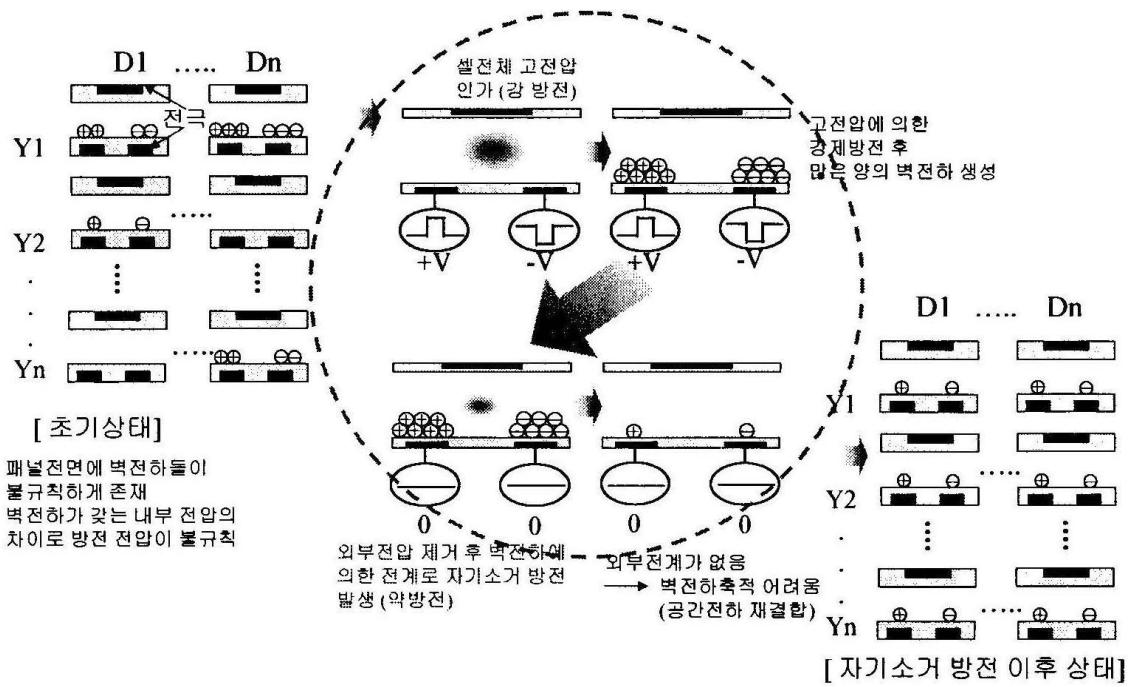

초기화 기간은 패널전면의 전기적 상태를 균일하게 해주는 기간으로 ①, ②의 상태로 나타낼 수 있다. 먼저 그림 5의 ①은 패널전면의 모든 전극에 고전압을 인가하여 강제방전을 발생시킨다. 이후 ②는 고전압으로 인해 벽전하가 과도하게 축적되어 벽전하가 가지는 벽전압이 방전개시전압 이상이 되면서 자기소거방전이 발생되어 방전공간내부의 잔류 벽전하가 모두 소거된 상태이다. 또한 이 방전은 방전공간내부에 공간전하를 생성시켜 이후에 오는 어드레스 방전에도 도움을 준다.[8]

어드레스 기간은 PDP에 화상을 나타내고자 하는 셀의 선택을 위한 기간이다. 이 기간은 그림 5의 ③과 ④의 상태로 나타낼 수 있다. Scan전극에는 어드레스 기간동안 Scan펄스를 순차적으로 계속해서 인가한다. 이때 Data 전극에는 화상정보에 따라 필요한 전극에만 선택적으로 펄스전압을 인가하여 ③과 같이 동 타이밍상에 Scan과 Data전극에 전압이 인가된 경우에만 두 전압의 합이 방전개시 전압보다 높아지면서 방전이 발생된다. 이 방전이 발생된 셀은 ④와 같이 방전공간 내부의 각 전극위에 전하들이 축적된다. 이와 같이 유전체 위에 축적된 전하들을 벽전하라고 한다.

표시방전유지 기간에서는 패널전면의 X와 Y의 표시전극에 교대로 Sustain펄스를 인가하여 벽전하가 축적된 셀에서만 표시방전을 유지시킨다.

이때 Sustain펄스의 전압은 벽전하가 축적된 셀의 벽전압과의 합이 방전 개시전압이 될 수 있도록 방전 개시전압보다 낮게 설정한다. 따라서 Sustain 펄스가 인가되더라도 벽전하가 생성되지 않은 셀에서는 방전개시 전압 이하의 전계가 인가되므로 방전이 발생되지 않게 된다. 그럼 ⑤는 Y전극에 폭이 넓은 펄스를 인가하여 최초의 표시방전을 발생시킨 후 충분한 벽전하 축적에 도움을 준 것이다. 방전직후 ⑥에서처럼 벽전하는 역극성으로 재축적 된다. 다음의 Sustain전압을 ⑦과 같이 X전극에 인가해주면 표시방전 이후 ⑧과 같이 벽전하가 반전된다. 이와 같이 표시전극에 교대로 전압을 인가하면서 반전된 벽전하의 벽전압이 표시방전을 유지할 수 있도록 도움을 주는 것을 벽전하에 의한 Memory 효과라고 한다. 표시방전기간 이후 ⑨와 같은 폭이 좁거나 전압이 낮은 Erase펄스를 인가하여 약한 방전을 발생시키면 방전이후 벽전하가 축적되지 못하고 ⑩에서처럼 공간전하 재결합에 의해 소멸된다.

이 구동 방식은 위와 같이 각 기간을 시간적으로 분리하여 설치하고 각각의 방전을 독립적으로 제어하므로 어드레스 디스플레이 분리 구동법이라고 부른다.

그림 4. ADS 구동방식의 타이밍도

Fig. 4. The timing chart of ADS driving methode

그림 5. ADS 구동법에 의한 방전 제어과정

Fig. 5. A discharge control course by ADS driving method

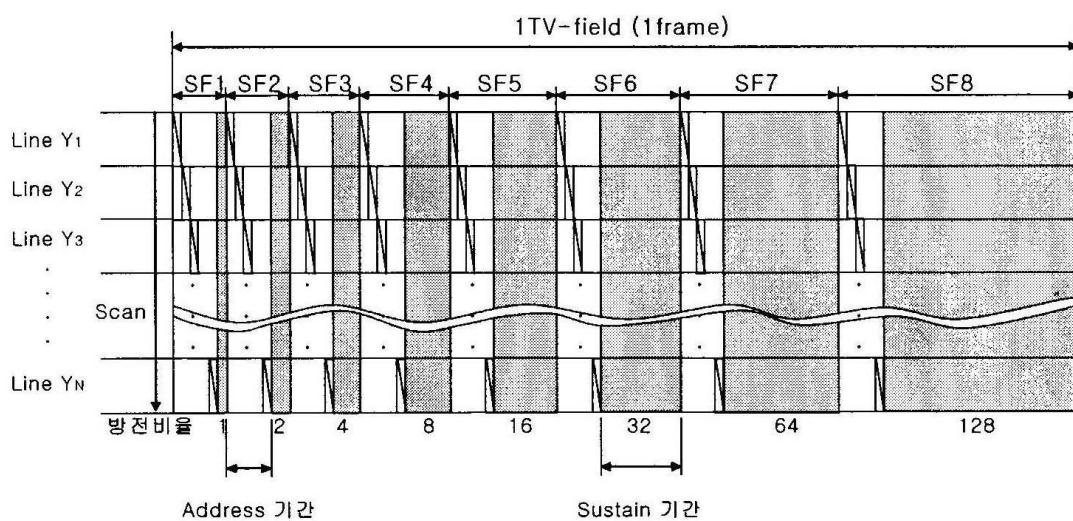

#### 4. PDP의 화상구현 원리

디스플레이 소자에 동화상을 구현하기 위해서는 1초에 60개의 정지 화상을 연속적으로 보내야 한다. 그리고 각각의 정지 화상을 24bit(적 8bit, 녹 8bit, 청 8bit)로 표현하기 위해서는 각 화소를 256단계의 계조로 광량을 조절하여야 한다.[9] 1개의 정지화상은 1TV field라고 한다. PDP상에서의 계조표현은 각 SF가 가지는 표시발광의 방전횟수를 제어함으로서 나타낼 수 있다.

그림 6은 256단계의 계조를 표현할 수 있는 ADS 구동법의 1TV-field 구조이다. PDP에서는 계조 표현을 위해 하나의 TV-field를 다수의 SF로 나눈다. 예를 들어 8bit 256 단계로 계조표현을 하기 위해 8개의 SF로 나누면 각각의 SF는 SF1, SF2, SF3,...SF8로 표시되고 각각의 SF가 가지는 방전유지시간의 비율은 SF1=2<sup>0</sup>(1), SF2=2<sup>1</sup>(2) SF3=2<sup>2</sup>(4), SF4=2<sup>3</sup>(8), SF5=2<sup>4</sup>(16), SF6=2<sup>5</sup>(32), SF7=2<sup>6</sup>(64), SF8=2<sup>7</sup>(128)로 설정된다. 이렇게 설정된 방전유지시간의 비율이 방전횟수의 비율이 되며 각 SF가 갖는 방전 횟수의 합이 각 화소가 갖는 휘도가 된다. 각각의 SF는 시간적으로 분리되어 있으나 1개의 TV-field 시간인 16.6ms 안에서 SF의 표시방전 시 발생되는 빛의 누적된 양이 우리 눈에 인식되므로 각 SF의 발광시간을 제어하면 256단계의 계조를 표현할 수 있다.[10][11][12]

그림 6. PDP의 계조구현 원리도

Fig. 6. A gray scale realization scheme of PDP

### III. PDP 구동 실험장치의 개발

PDP 패널에 인가하는 고전압펄스들을 제어하기 위해서는 펄스 타이밍을 발생시키는 로직 회로를 제작하여야 한다. 기존의 PDP 구동실험장치들은 펄스 설계를 위해 범용의 로직 gate IC들을 사용하였다. 이러한 IC들을 사용하게 되면 간단한 펄스라 할지라도 수십 개 이상의 로직 gate IC를 사용하여야만 한다. 그리고 펄스의 개수가 많아지거나 펄스의 타이밍 등이 변하게 되면 이미 물리적으로 만들어진 로직 회로부를 해체하여 새로 제작하여야만 하였다. 이와 같은 기존의 방법은 실험을 위한 초기준비 시간이 많이 소요되고, 각각의 범용 IC들을 물리적으로 접속하는 과정에서 많은 노이즈가 발생되어 펄스 품질을 저하시킨다. 그러나 PLD (Programmable Logic Device)를 이용한 로직회로부를 사용하게 되면 별도의 물리적인 작업 없이 컴퓨터상의 디지털 시스템 설계용 프로그램만을 이용하여 손쉽게 펄스를 변경하거나 추가시킬 수 있어 단시간 내에 실험환경 구현이 가능하며 신뢰성 또한 높다.

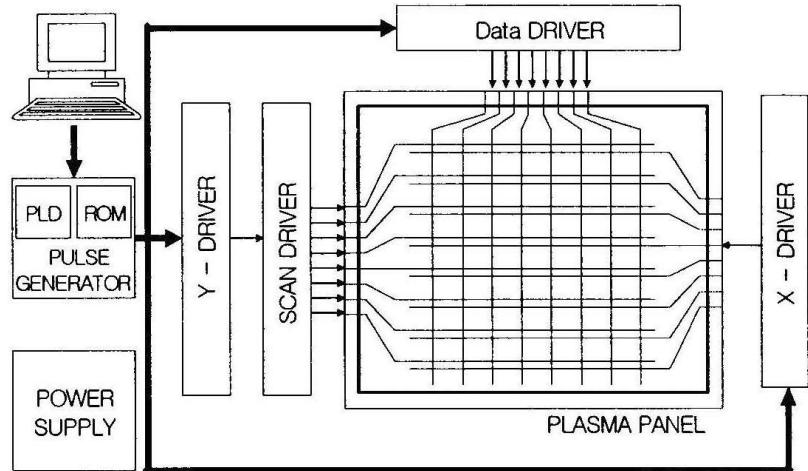

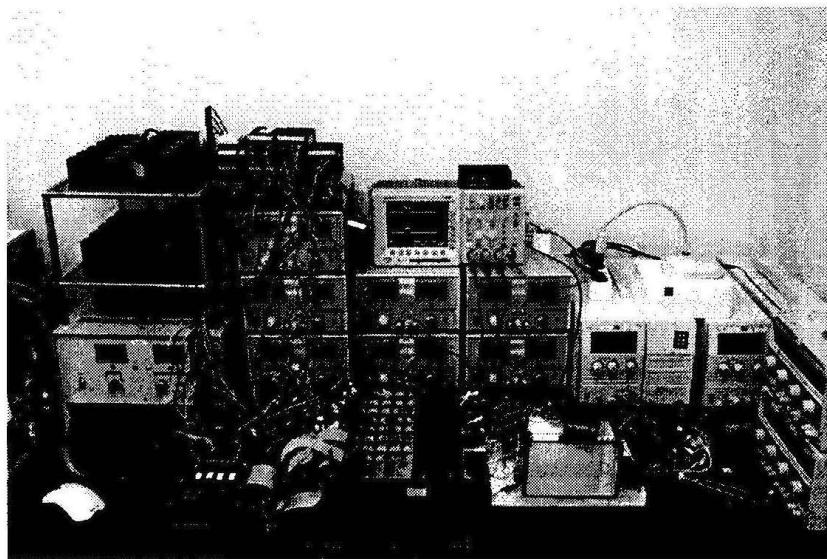

그림 7은 실험을 위해 제작된 PDP 구동실험 장치의 구성도와 실제 사진이다. 이 실험 장치는 크게 퍼스널 컴퓨터와 PLD가 내장된 펄스 발생기, Data, X, Y, Scan을 위한 고전압펄스를 발생시키는 구동 드라이버, 그리고 펄스발생기와 드라이버들을 위한 전원부로 구성되어 있다. 퍼스널 컴퓨터에는 디지털 시스템 설계를 위한 소프트웨어가 있어 이 소프트웨어를 이용하여 각종 드라이버를 제어하는 구동 펄스의 타이밍을 설계, 시뮬레이션 할 수 있다. 이렇게 설계된 구동 펄스는 PC의 병렬포트를 통하여 펄스 발생기의 PLD에 프로그래밍 된다.

(a) 구성도

(b) 실제사진

그림 7. PDP 구동실험 장치의 구성도와 실제사진

Fig. 7. The block diagram of PDP drive system and actual picture

## 1. 펄스 발생부

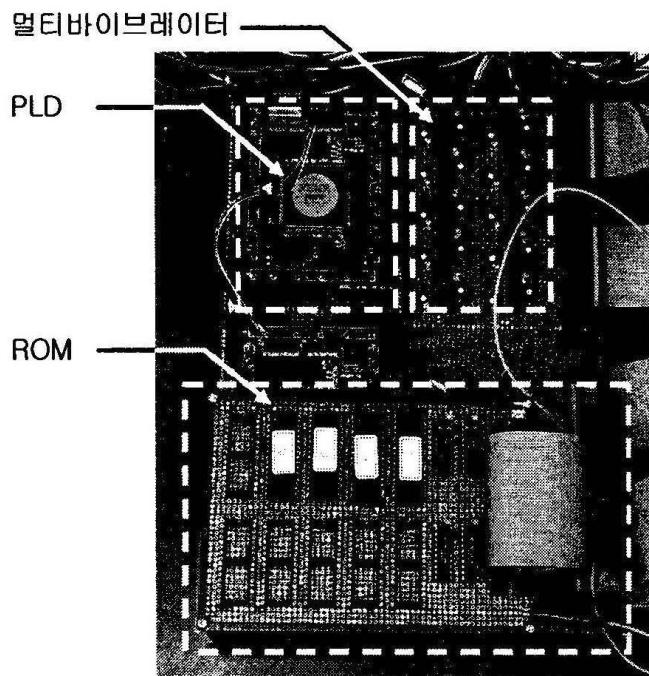

그림 8은 제작된 펄스발생기의 사진이다. 펄스발생기는 고전압 Driver를 위한 신호를 생성하며 크게 PLD제어부와 ROM제어부, 그리고 멀티바이브레이터부로 나눌 수 있다. PLD제어부는 2개로 구성되어있으며 상단의 PLD는 X, Y, Scan펄스를 담당하고 하단은 Data펄스의 입·출력을 담당한

다. 제작에 사용된 PLD는 ALTERA사의 FLEX 10k 100ARC-1이며 10만 게이트까지 생성이 가능하다. 초기실험을 위해서는 그다지 많은 게이트 수를 요구하지 않지만 추후 6인치패널 전면에 계조 패턴을 구현하기 위해서는 용량이 10만 게이트 정도는 되어야 하므로 FLEX 10k 계열을 선정하였다.

ROM 제어부에서는 ROM의 Data를 읽어 들여 PLD로 전송하는 역할을 한다. ROM의 영상정보 입력은 별도의 ROM-writer 장치를 사용한다. 멀티 바이브레이터부는 PLD로부터 변환된 로직 신호의 펄스폭과 간격을 ns단위로 미세 조정할 수 있다.

그림 8. PLD를 사용한 타이밍 펄스 발생부

Fig. 8. The timing pulse generator with PLD

## 2. 구동 회로부

그림 9(a)와 9(b)는 PDP 구동실험장치의 고전압 FET 쌍으로 되어있는 구동 드라이버 회로부의 모습과 회로도이다. X, Y 및 Data와 Scan 드라이버 부는 펄스발생부로부터 로직 신호를 전달받아 PDP를 구동하는데 필요한 고전압 펄스를 발생시키는 역할을 하며 P형과 N형의 FET(Field Effect

Transistor)의 조합으로 구성된 다수의 FET 스위칭 회로부로 구성되어 있다.

전원부는 펄스발생부의 동작을 위한 1개의 DC 5V 전원과 FET를 제어하는 포터커플러 구동을 위한 다수의 DC 12V 전원, 그리고 PDP 구동을 위해 각 전극에 인가하는 고전압 펄스를 만드는 가변 DC 전원들로 구성 되어 있다.

(a) 실제 사진

(b) 회로도

그림 9. 고전압 스위칭 회로부

Fig. 9. The circuit of high-voltage FET switches

### 3. PDP 구동을 위한 타이밍 펄스의 설계

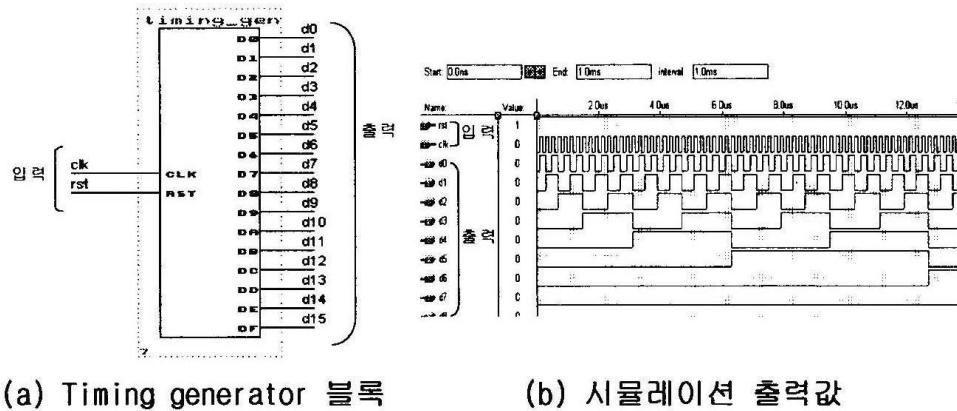

PDP 구동을 위한 타이밍 펄스의 설계는 디지털 시스템설계 프로그램을 사용하였다. 본 논문에서는 펄스타이밍의 손쉬운 설계를 위해 가장 기본이 되는 3가지 논리 블록들을 개발하였다. 각 논리 블록에는 별도의 입력을 설정할 수 있는 binary 스위치들이 있으며, 이 스위치들의 입력제어와 함께 기본 논리게이트들을 적절히 조합하면 생각할 수 있는 모든 펄스의 타이밍 설계가 가능하다. 이 논리 블록들은 블록의 역할에 따라 Timing generator,

Pulse generator, Window generator로 각각 이름을 붙였다. 그림 10은 Timing generator의 블록도(a)와 입력 값에 따른 펄스의 출력(b)을 나타내었다.

Timing generator는 펄스 설계의 가장 기본이 되는 블록으로 2개의 입력으로 16개의 출력을 발생시킨다. 입력중의 하나는 펄스발생기의 오실레이터 clock이며 다른 하나는 출력 펄스의 주기를 결정해주는 reset펄스이다. 16개의 출력은 각각 오실레이터 clock을 차례로  $2^1 \sim 2^{16}$  배한 연속적인 펄스가 발생된다. 여기서 발생된 펄스를 기본 단위펄스로 이용할 수 있다. 이 실험에서는 10MHz의 오실레이터를 사용하였다. 그러므로 가장기본이 되는 단위펄스는 펄스폭이  $100 * 2^1$  ns 가 된다.

그림 10. Timing generator 블록과 시뮬레이션 출력값

Fig. 10. The timing generator block and the results of simulation

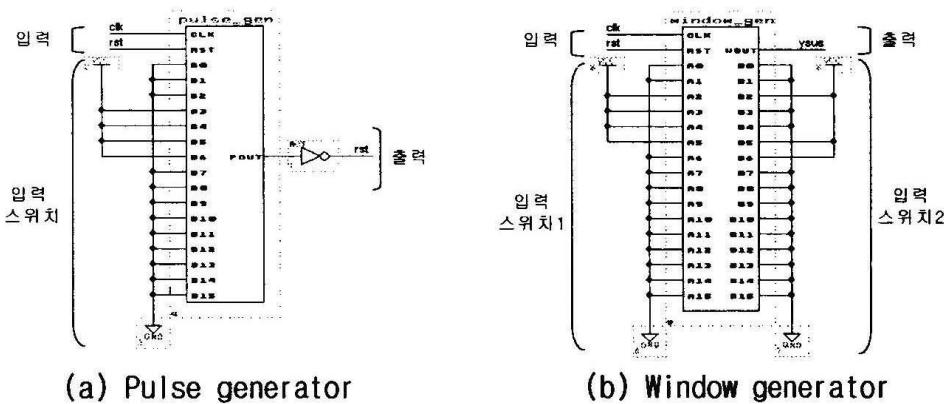

그림 11(a)는 Pulse generator 블록의 그림이다. Pulse generator는 입력된 펄스폭의 2배가 되는 펄스를 원하는 위치에 발생시킬 수 있다. 그림에서 볼 수 있듯이 2개의 펄스 입력단과 16개의 스위치, 그리고 1개의 출력 단이 있다. 그림 11(b)는 Window generator의 블록이며 Window generator는 펄스폭이 넓은 펄스를 설계하는데 이용된다. 그림에서 볼 수 있듯이 2개의 펄스 입력단과 2개의 그룹으로 나뉜 입력 스위치단, 그리고 1개의 출력 단이 있다.

펄스의 폭은 입력 펄스로써 제어할 수 있으며 펄스 위치의 조절은 16개의 스위치를 ON/OFF 하여 결정할 수 있다. 이 스위치의 입력 값은 발생시키고자 하는 타이밍상의 위치(시간)를 입력 펄스폭으로 나누어 그 값을 이진 수로 변환하여 차례로 인가하면 된다.

그림 11. Pulse generator와 window generator의 블록도

Fig. 11. Blocks of pulse generator and window generator

그림 12는 PC상에서 실제로 시뮬레이션한 출력 값을 그대로 캡춰한 그림이며 ③번 출력은 Pulse generator의 출력 값이다. Pulse generator는 주로 발생된 펄스의 주기를 만드는데 사용할 수 있다. 그림 11의 (a) 입력 스위치 값을 “0000000001111000”로 주면 출력펄스의 위치가  $200\text{ns} * 120 = 24\mu\text{s}$  인 것을 확인할 수 있다. ( $0000000001111000_{(2)} \rightarrow 120$ )

펄스의 제어는 2개의 독립된 스위치그룹들로 한다. 1개의 스위치 그룹은 16개의 스위치로 구성되며 하나의 스위치 그룹은 펄스가 상승되는 위치를 결정하며 다른 하나의 그룹은 펄스가 하강하는 위치를 결정한다. 스위치의 입력은 Pulse generator와 마찬가지로 타이밍상의 위치를 입력 펄스폭으로 나누어 그 값을 이진수로 변환시켜 각각 차례로 인가하면 된다. 그림 11(b)를 보면 1입력 “0000000000111100”, 2입력 “0000000001100100”을 인가한 것을 볼 수 있으며  $0000000000111100_{(2)} \rightarrow 60$  ( $200\text{ns} * 60 = 12\mu\text{s}$ ),  $0000000001100_{(2)} \rightarrow 100$  ( $200\text{ns} * 100 = 20\mu\text{s}$ )로 12us에서 상승하여 20us에서 하강한 것을 그림 12의 ②번 출력그림으로 확인할 수 있다. 위 출력 펄스들은 Pulse generator를 이용하여 Rst(reset)펄스를 설계하였으며 그 펄스가 Window generator에서 만들어진 펄스의 주기가 된다.

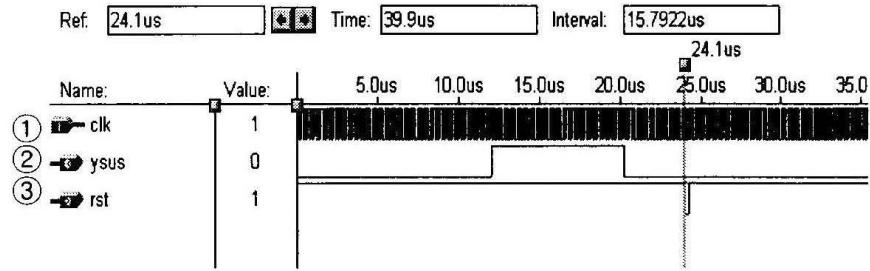

그림 13은 PDP구동을 위해 실제로 사용된 Sustain 펄스를 설계한 블록도이다. Sus\_unit 블록은 그림 11을 묶어 하나의 블록으로 만들었으며 이 블록에서 출력되는 Ysus 펄스와 또 다른 Window generator에서 발생된 펄스를 AND 시켜 Sustain 펄스를 설계하였다. 이 블록에서 설계된 펄스의 출력은 그림 14에서 볼 수 있다.

- ① clk : 기본단위 펄스폭 100ns, 주기 200ns

- ② ysus : Window generator의 출력값, 펄스폭6us,주기 24us

- ③ rst : Pulse generator의 출력값, 펄스폭 200ns

그림 12. Pulse generator와 window generator의 블록의 시뮬레이션

Fig.12. The simulation result of pulse generator and Window generator block

그림 13. sustain 펄스를 설계한 블록도

Fig. 13. A block diagram of designed sustain pulse

- ① rst : PDP구동시 Tv-field를 결정

- ② ysus\_win : Sustain 펄스의 개수를 결정

- ③ ysus : 발생된 기본단위의 sustain 펄스

- ④ sustain : 발생된 Sustain 펄스

- ⑤ sus\_rst : Sustain 펄스의 기본주기 결정

그림 14. Sustain 블록의 출력 시뮬레이션

Fig. 14. A simulation result of sustain block

#### 4. 측정장비

아래의 그림 15는 실제 실험에 사용한 장비들로 각각의 기능과 특징을 요약하여 나타낸 것이다. 광 검출기는 PDP의 방전시 발생되는 광을 Photo diode로 검출하여 오실로스코프상의 파형으로 나타내준다. 이 장치를 이용함으로써 PDP의 구동시 오방전 유무를 확인할 수 있다. 휘도계는 PDP방전 면의 휘도를 측정하여  $[cd/m^2]$ 으로 나타내주는 장치이다. CCD 카메라는 PDP화면상에 동영상 또는 정지화상의 구현시 Frame 단위의 연속촬영을 하여 화상 Data를 PC상에서 분석할 수 있게 해주는 장치이다.

##### [ 광 검출기 ]

PDP의 방전시 광을 Photo diode로 검출

하여 파형으로 나타냄

파장대역 : 400 ~ 1060 nm ( 830nm )

HAMAMATSU C6386

##### [ 휘도계 ]

PDP의 방전광을 측정하여  $[cd/m^2]$  로

나타냄

MINOLTA LS-110

##### [CCD 카메라]

PC로 동영상 및 정지화상 관찰

화소수 : 27만 화소 color

1mm 접사 ( 10배 확대 )

SONY CCD- PC1

그림 15. PDP 측정장비

Fig. 15. The equipment for the measurement of PDP

#### IV. PDP의 교류구동 특성 및 평가

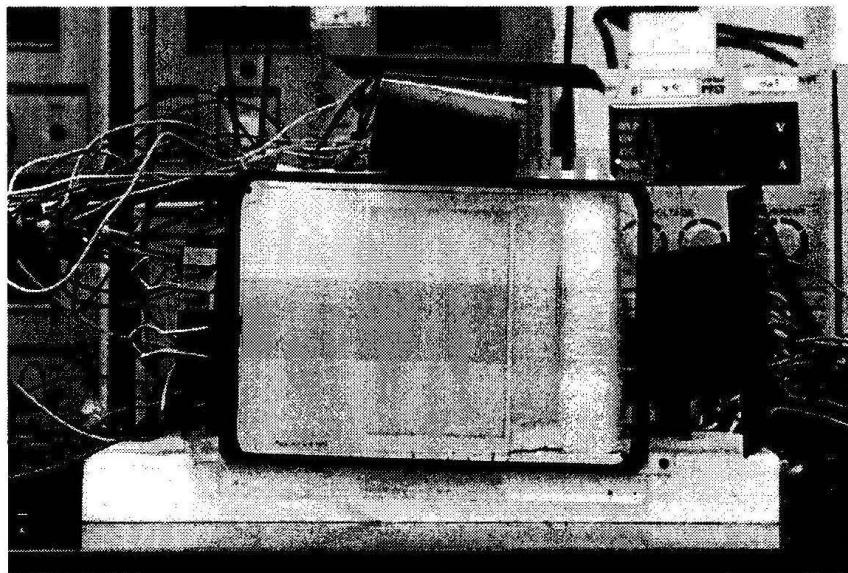

본 실험에서는 PDP의 교류구동 특성을 알아보기 위하여 상용의 ADS 구동방법을 사용하였으며 구동타이밍을 실험에 맞게 설계하였다. 그림 16은 실제실험에 사용한 3전극 면방전 구조의 패널이다. 전극의 구조는 그림 2의 패널구조와 동일하며 표시전극간 거리는 0.1mm이며 각 표시전극은 0.26mm의 폭을 가진다. Data전극의 폭은 0.1mm이며 상판유리의 표시전극과는 0.12mm 간격으로 떨어져 있다. 방전공간 내부에는 Ne+ 4%Xe의 혼합가스가 500Torr의 압력으로 주입되어 있다.

그림 16. 실제실험에 사용한 3전극 AC PDP

Fig. 16. The three electrodes AC PDP which uses at actual experiment

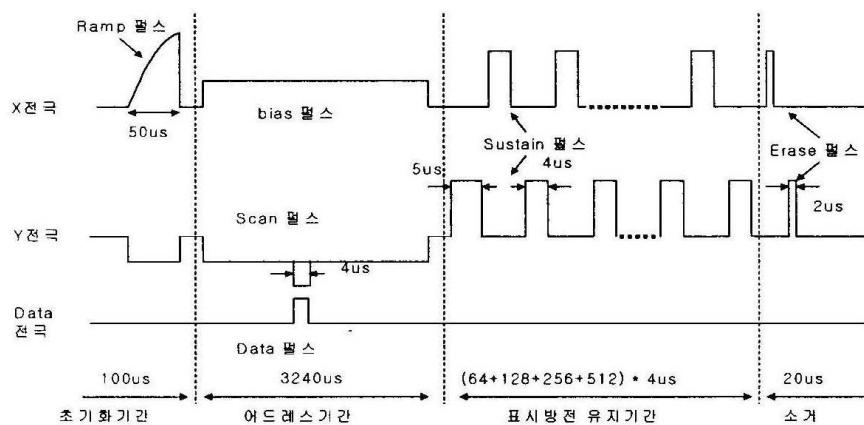

그림 17은 실제 실험에 사용된 서브필드의 펠스타이밍 구조이다. 전술한 바와 같이 하나의 SF는 초기화, 어드레스, 표시방전유지의 3개의 기간으로 나누어져 있다. 초기화 기간에서는 불균일한 잔류 벽전하를 효과적으로 제거하기 위해 높은 전압의 Ramp펄스를 패널 전면에 인가하여 패널 전면의 전기적인 상태를 균일하게 만들 수 있도록 하였다.

어드레스 기간에서는 Y전극에 Scan펄스를 Data전극에 Data펄스를 인가하여 화면 중 표시할 셀들을 순차적으로 방전시켜 벽전하를 생성시키도록

하였다. 표시방전 유지기간에서는 X와 Y 전극에 공통으로 표시방전 펄스를 교대로 인가하여 어드레스 기간에서 벽전하가 생성된 셀들의 방전을 지속 시켜준다. 각 SF에서는 표시방전의 횟수를 조절하여 각 계조레벨에 상응하는 밝기를 나타낸다. 표시방전 유지기간 이후 폭이 좁은 Erase 펄스를 X와 Y전극에 각각 인가하여 표시방전을 소거 시켜준다.

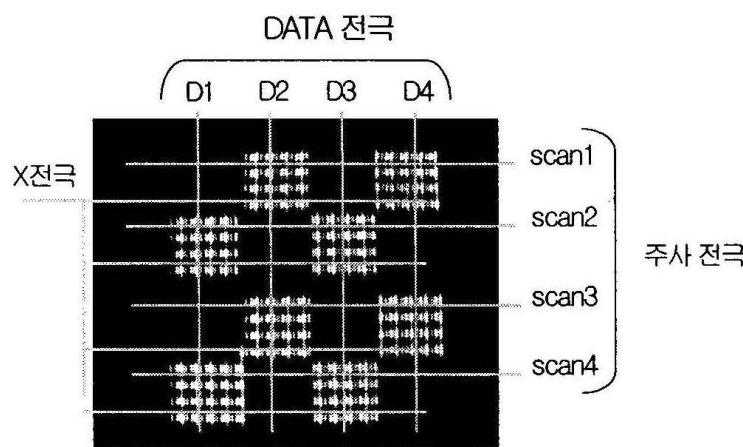

그림 18은 패널 방전면의 평균휘도 측정방법을 나타낸 그림이다. 총 방전 면은 16개의 소면적 영역으로 구성되어 있으며 각각의 영역은 휘도 측정을 용이하게 하기 위해 data 전극 3라인, scan 전극 2라인이 교차되는 지점으로 하였다. 휘도의 측정은 각 방전 영역 간을 한 칸씩 건너뛰어 바둑판 문양으로 방전시킨 8개의 영역을 각각 휘도계로 측정하여 그 평균값을 취하였다.

그림 17. 실제 실험에 사용한 sub-field의 구조

Fig. 17. The structure of the sub-field which uses at actual experiment

그림 18. 휘도의 측정 방법

Fig. 18. A measurement method of the brightness

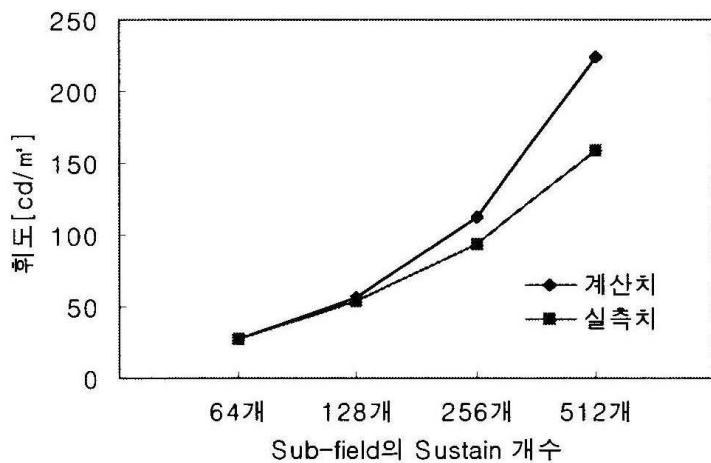

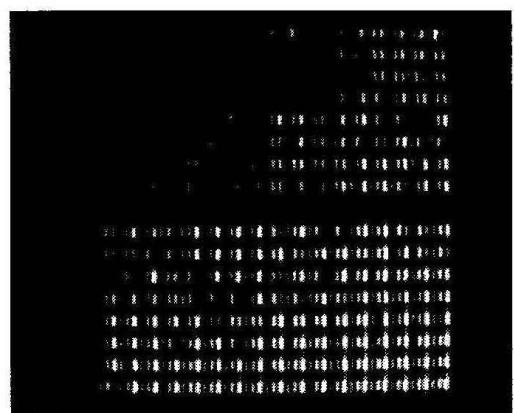

그림 19는 각 서브필드내의 표시방전 유지펄스의 개수에 따른 휘도의 계산치와 실제측정치를 나타낸 그림이다. 16계조를 표현하기 위해 1 TV-field를 4개의 SF로 나누었으며 각 SF의 표시방전 유지펄스 개수는 SF 1부터 SF 4까지 각각  $2^6$ ,  $2^7$ ,  $2^8$ ,  $2^9$ 개로 설정하였다.

SF 1의 방전 휘도를 휘도계로 측정한 결과 패널의 특성에 따라 다르겠지만 본 실험에 사용된 실험용 패널에서는  $28[\text{cd}/\text{m}^2]$ 로 측정되었다. 이를 기본으로 각 SF의 휘도의 증가 비율이 2배수 이어야 하나 실제로 측정된 휘도는 표시방전 유지펄스의 개수가 증가함에 따라 더 낮은 비율의 증가를 보였다. 이는 기본적으로 초기화 방전시 발생되는 광에 의한 영향과 패널의 특성에 기인하는 것으로 보여 지며 이 같은 현상을 없애기 위해서는 표시방전 유지펄스의 개수를 조절하여 적절한 계조레벨의 비율을 패널에 맞게 재설정하여야만 한다.

그림 19. Sub-field의 표시방전 유지펄스의 개수에 따른 휘도

Fig. 19. The brightness according to sustain number of sub-field

## 1. 초기화기간의 방전특성

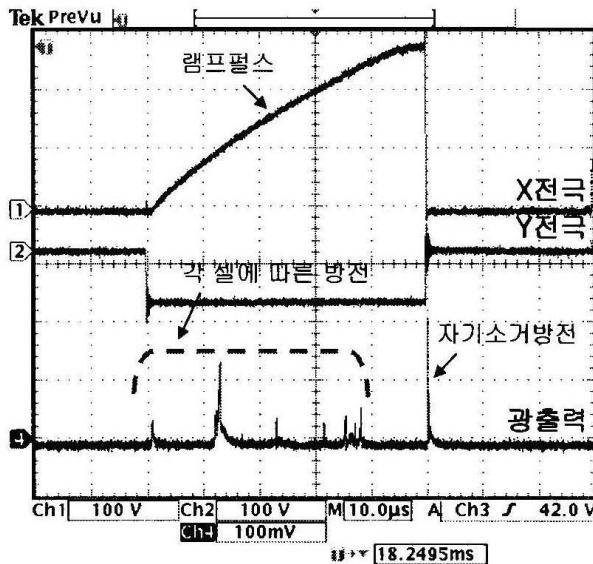

실제 패널전면의 각 셀들은 불균일한 잔류 복전하를 가지고 있다. 따라서 셀의 전기적 상태에 따라 차등전압을 인가하여 각각 적정전압에서 약방전시키고, 이후 패널전면에 고전압을 인가하여 자기소거방전을 시키는 것이 패널 균일화에 더욱 효과적이다. 그림 20은 초기화 기간동안 패널전면에 인

가된 램프펄스와 그때 다수의 방전셀에서 발생되는 방전광들을 측정한 그림이다. 광출력을 보면 각 전압레벨에 따라 광출력이 다르게 나타나는 것을 볼 수 있으며 램프펄스의 종료시점에서 자기소거 방전이 발생된 것을 볼 수 있다. 이와 같은 램프 펄스는 패널 전면의 전기적 상태를 균일화하는데 효과적이며 불필요한 방전을 최소화하여 배면광에 의한 화질저하가 감소되므로 실제 양산되고 있는 PDP제품들에 사용되고 있다.

그림 20. 램프펄스에 의한 광출력

Fig. 20. The light output by the ramp pulse

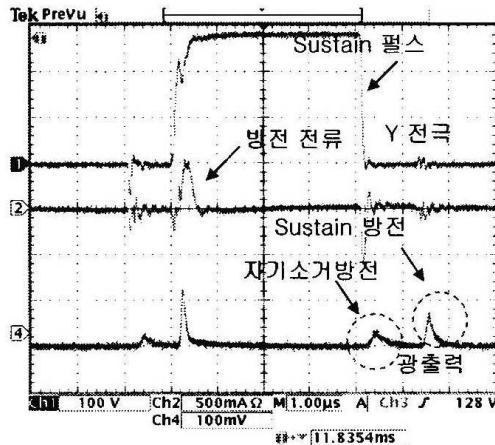

그림 21은 자기소거방전의 동작 메커니즘이다. 위에서 언급한 바와 같이 초기상태의 각 셀들은 불균일한 벽전하를 가지고 있다. 이 경우 벽전하가 가지는 내부전압의 차이로 방전전압이 불규칙하다. 초기화기간에 높은 전압을 패널 전면에 걸쳐 인가하면 각 셀들의 방전공간은 강한 전계로 인해 강제 방전이 발생하게 된다. 강제 방전이후 생성된 많은 양의 공간전하들은 방전직후 음극과 양극에 쌓여 많은 벽전하로 축적되어진다. 이후 외부전계가 사라지면 벽전하들이 가지는 전계로 인해 다시 한번 방전하게 되며 이 때 생성된 공간전하들은 외부 전계가 없으므로 벽전하로 축적되지 못하고 재결합하여 소멸된다. 이 방전이후 패널 전면의 각 셀들은 벽전하게 거의 없는 동일한 전기적 상태를 가지게 된다. 이와 같이 고전압에 의한 강제방전 후 발생되는 방전을 자기소거방전이라고 한다.

그림 21. 자기소거방전

Fig. 21. The self erase discharge

## 2. 각 구동 펄스의 동작 마진정의 및 특성평가

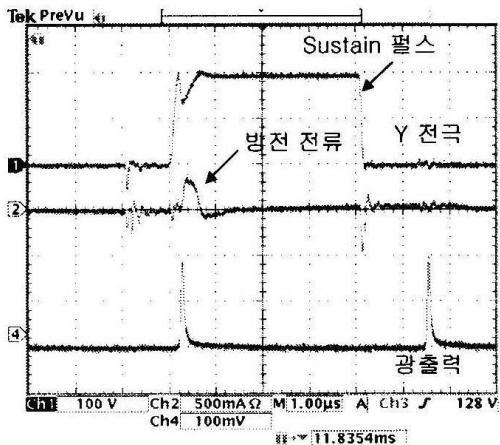

그림 22(a)는 data 펄스폭이  $4\mu s$ , 표시방전 유지펄스 폭이  $4\mu s$ 일 경우 모든 화소가 안정적인 표시방전을 하는 최소의 표시방전 유지펄스 전압을 인가한 경우이다. 22(b)는 안정적인 표시방전 이후에 표시방전 유지펄스 전압을 계속 증가시켜 과전압에 의한 자기 소거 방전을 유도한 경우이다. 그림 22(a)와 22(b)의 전류의 형태를 보면 모두 방전이 끝난 이후에도 전류가 지속되는 것을 볼 수 있는데 이 전류는 방전이후 벽전하 축적에 의한 전류로 추정할 수 있다. 그림 22(b)에서는 높은 펄스 전압으로 인한 과도한 방전 이후 방전이 감소된 것을 볼 수 있다. 실제 패널 면에서도 불안정한 방전이 측정되었다.

이것은 다음과 같이 추정할 수 있다. 과방전으로 인해 생성된 많은 양의 공간전하들이 방전이후 펄스전압에 의해 벽전하로 축적되어진다. 이후 펄스 전압이 제거되면 높은 벽전압으로 인해 스스로 방전이 되는 자기 소거 방전이 발생 되어진다. 따라서 벽전하량이 감소되면서 다음 펄스전압 인가시 방

전이 불안정 해지는 것이다.[13]

(a) 안정된 표시방전 유지시

(b) 과방전에 의한 벽전하 소거

그림 22. 표시방전 유지펄스 전압에 따른 방전의 변화

Fig. 22. The variation of discharge according to voltage of sustain pulse

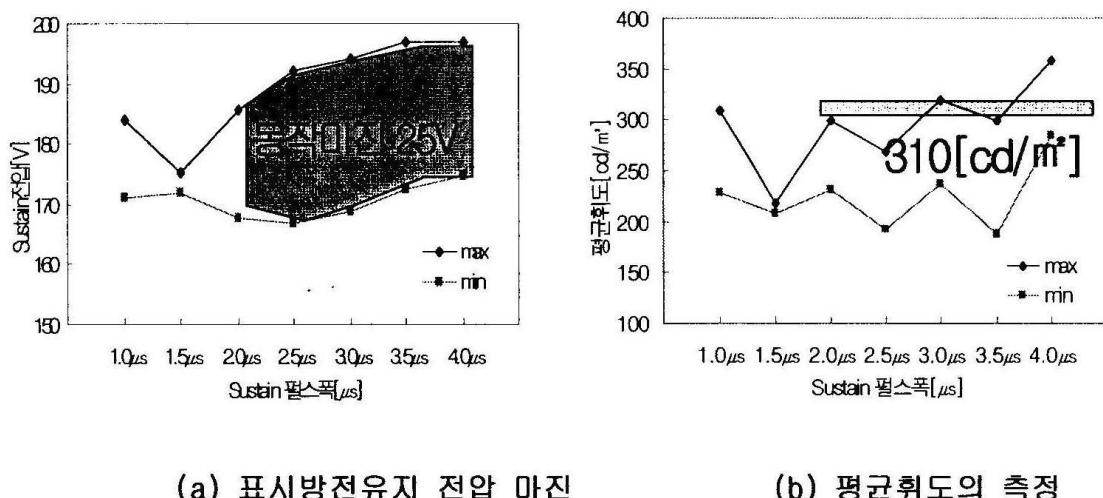

그림 23(a)는 어드레스 펄스폭을  $4\mu\text{s}$ 로 고정 후 표시방전 유지펄스 폭을  $1\mu\text{s} - 4\mu\text{s}$  까지  $0.5\mu\text{s}$  단위로 변화 시키면서 그 때의 표시방전 전압마진을 측정한 그래프이다. 전압의 마진을 측정하기 위해 표시방전의 유지 상태를 육안으로 보고 평가를 하였다. 방전 최소전압-그림 22(a)상태 (min)는 전압을 서서히 증가시켜 패널 중 어드레스 방전이 발생된 모든 셀들이 안정된 표시방전을 유지하는 최소의 전압으로 설정하였으며 방전 최대전압-그림 22(b)상태 (max)는 표시방전유지 전압에서 전압을 계속 증가시켜 과방전에 의한 자기소거 방전으로 벽전하가 일부 소실되어 방전이 불안정해지기 직전의 전압으로 설정하였다. 이때의 동작마진은 아래 수식과 같다.

$$\text{표시방전 전압마진} = \text{과방전 발생직전전압} - \text{Sustain 최소전압} \quad \dots \quad (1)$$

최대 방전전압은 표시방전 유지펄스 폭이 좁아짐에 따라 전압이 낮아지는 것을 볼 수 있다. 이는 벽전하 보다 방전직후 생성된 공간전하가 자기 소거 방전에 더 큰 영향을 주기 때문이다.[13] 따라서 펄스의 폭이 좁을수록 방전 공간내부에 더 많은 공간전하가 존재하므로 최대 방전전압은 더 낮아진다는 것을 알 수 있다. 그러나 펄스폭이  $1.5\mu\text{s}$  까지는 이 같은 현상이 측정되어지나 펄스폭이 더 좁은  $1\mu\text{s}$ 인 경우는 오히려 방전 전압이 더 높게 측정되는 현상이 있다.

정이 되었다. 이것은 펄스의 폭이 좁아지면 벡전하의 축적은 충분하지 않으나 방전공간내의 풍부한 공간전하의 영향으로 표시방전이 유지되는 것으로 추정되어진다.

최소 방전전압역시 최대전압과 비슷한 결과를 보여 주는데 펄스폭이  $1.5\mu s$  이전의 방전개시전압이 높게 측정되는 것으로 보아 펄스폭이  $1.5\mu s$ 보다 좁은 폭에서는 충분한 벡전하 축적이 어려워 방전에 도움을 주지 못한다는 것을 알 수 있다.

그림 23(b)는 표시방전 유지펄스 폭에 따른 평균휴도의 값을 측정한 그래프이다. 그림에서와 같이 표시방전 유지펄스 폭이  $4\mu s$  인 경우 가장 밝은 휴도가 측정되었으며  $1.5\mu s$  의 경우 가장 낮은 휴도가 측정되었다. 그 외의 다른 펄스폭에서는 휴도의 차이가 미미한 정도로 측정되었다. 이상의 실험에서 충분한 동작마진을 고려한다면, 표시방전유지 펄스의 폭은  $2\mu s$ 까지 감소시킬 수 있으며  $2\mu s$ 에서 185.6V,  $2.5\mu s$ 에서 192V,  $3\mu s$ 에서 194V,  $3.5\mu s$ 와  $4\mu s$ 에서 197V로 각 펄스의 폭에 따라 전압을 가변시켜 주면 평균적으로  $310[cd/m^2]$ 로 펄스폭에 따른 휴도의 차이가 거의 없는 안정적인 표시방전이 가능하며 동작마진은 25V 정도로 측정되었다.

그림 23. 표시방전유지 펄스폭 변화에 따른 전압 마진과 평균휴도

Fig. 23. The operation margin and brightness by change of sustain pulse width

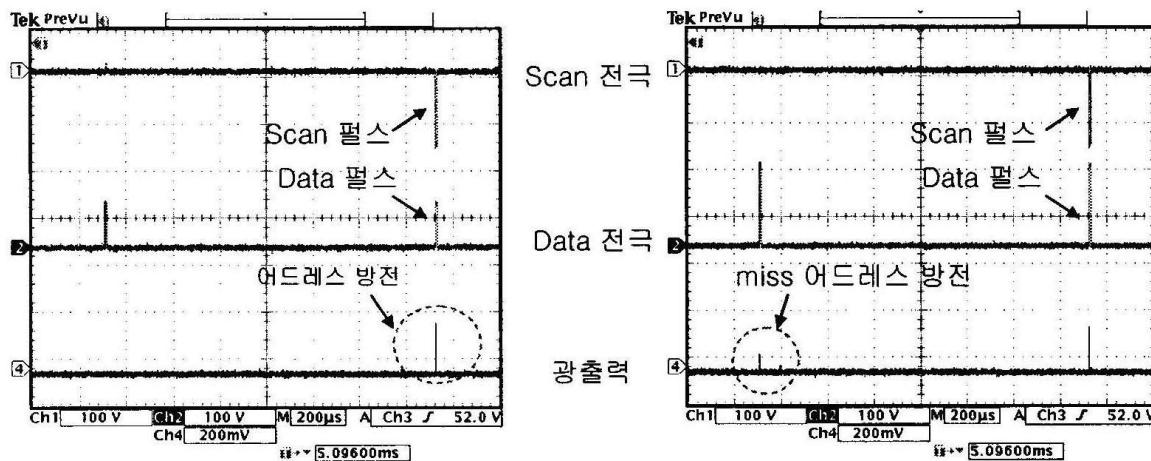

그림 24(a)는 어드레스 방전에 의해 안정된 표시방전을 하는 최소의 어드레스전압인가시의 어드레스 방전의 모습이며 24(b)는 과도한 어드레스전압

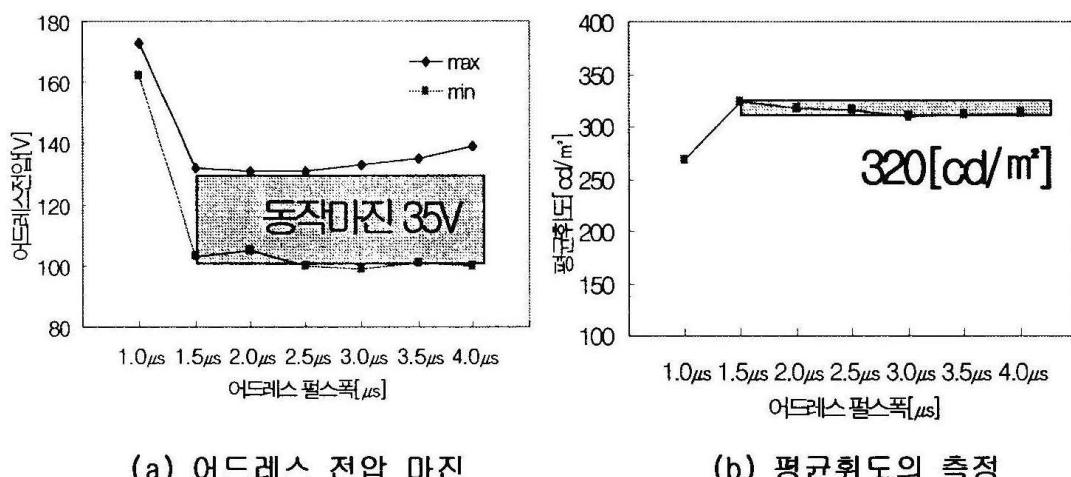

으로 인해 Scan펄스 없이 어드레스전압만으로 방전이 발생된 miss 어드레스 방전의 모습이다. 그림 25는 표시방전 유지펄스폭을  $4\mu s$ 로 설정하고 안정된 표시방전이 일어나는 전압조건으로 어드레스 펄스폭을  $1\mu s - 4\mu s$  까지  $0.5\mu s$  단위로 증가시키면서 그때의 어드레스 동작 마진과 표시방전의 휘도를 측정한 그래프이다. 이 실험에서도 표시방전 유지전압의 마진측정과 비슷하게 펄스폭이 좁아질수록 최대 전압이 낮아지는 특성을 보였다. 그러나 과전압으로 인한 어드레스 방전이 표시발광에 미치는 영향이 너무나 미세하여 육안으로 식별하기에는 무리가 있었다. 그래서 어드레스 최대전압은 어드레스 전압을 증가시켜 어드레스 방전이 발생되지 말아야 할 화소의 광을 측정하여 어드레스 오방전이 발생되기 직전의 전압으로 설정하였다. 이 때의 어드레스 전압마진은 아래 식으로 나타낼 수 있다.

$$\text{어드레스 전압마진} = \text{miss 어드레스 발생 직전전압} - \text{어드레스 최소전압} \dots \dots (2)$$

어드레스 최소방전 전압은 어드레스 전압을 인가하여 어드레스 방전으로 생성된 벽전하의 영향으로 표시방전이 유지되는 최소의 전압으로 설정하였다. 그림 25(a)는 어드레스 전압의 마진을 측정한 결과로써 펄스폭이  $1.5\mu s$  이상인 경우 동작마진이  $35V$ 정도로 거의 일정하게 측정되었다. 그러나  $1.5\mu s$ 보다 좁은 어드레스 펄스에서는 방전개시전압이 60%정도 상승하였으며 방전 마진 또한 절반 수준으로 떨어졌다. 그림 25(b)는 각 어드레스 펄스폭에 따른 최소전압 인가시 표시방전의 광출력을 측정한 결과이다. 펄스폭이  $1.5\mu s$ 를 기준으로 넓어지는 경우 표시방전 유지펄스가 1024개에서 평균적으로  $320[\text{cd}/\text{m}^2]$ 의 휘도로 거의 동일하였으며 그보다 좁은 경우 휘도는  $100[\text{cd}/\text{m}^2]$ 이상 감소하였다. 이러한 결과는 안정적인 표시방전에 도움을 줄 수 있는 어드레스 벽전하 축적시간은 최소  $1.5\mu s$ 이상이 되어야 한다는 것을 말해주며 그때의 어드레스 전압은  $100V - 135V$  사이로 방전마진이  $35V$ 정도가 된다.

(a) 어드레스 방전에 의한 표시방전시 (b) 과전압에 의한 miss 어드레스 방전시

그림 24. 어드레스 펄스 전압에 따른 방전의 변화

Fig. 24. The variation of discharge according to voltage of address pulse

(a) 어드레스 전압 마진

(b) 평균화도의 측정

그림 25. 어드레스 펄스폭 변화에 따른 전압마진과 화도의 측정

Fig. 25. The operation margin and brightness by change of address pulse width

그림 26은 안정적인 표시방전조건을 만족하는 어드레스 펄스폭 조건인 3  $\mu$ s를 적용하여 표시방전 유지펄스 폭을 1  $\mu$ s - 4  $\mu$ s로 변화시켜 가면서 각 경우의 어드레스 전압의 동작마진을 측정한 그래프이다. 좁은 펄스폭으로 벽전하의 축적이 어려운 펄스폭인 1.5  $\mu$ s이하를 제외하면 펄스폭 4  $\mu$ s까지 거의 모든 범위 내에서 어드레스 동작전압 마진이 일정한 것을 볼 수 있다. 이것은 어드레스 방전으로 최소한의 벽전하만 형성시켜 준다면 안정적인

표시방전을 얻을 수 있다는 사실을 말해준다.

그림 26. 표시방전유지 펄스폭에 의한 어드레스 동작마진

Fig. 26. The Operation margin of address voltage by change of sustain pulse width

본 실험에서는 3전극 면방전 구조의 PDP에 적용 가능한 최소의 펄스조건을 제시하였다. 이 펄스 조건을 가지고 사용가능한 SF의 개수와 그때의 최대 휘도를 좀더 구체적으로 알아보기 위하여 수식(3)을 만들어 보았다. 이 식에서는 다음과 같은 몇 가지 조건들을 포함하고 있다. 표준 TV의 규격에 따라 1TV-field의 시간은 16.6ms로 설정하였다.[9] 1TV-field의 각 SF에 포함된 초기화 기간은 설정에 따라 다르나 본 실험에서는 100μs를 할당하였다.

아래 식(3)의 16600μs는 1TV-field가 갖는 시간이며 Treset은 초기화에 필요한 시간이다. Nscan은 수평 주사선수의 개수이다. Tad는 어드레스 펄스폭이며 Tsus는 표시방전유지 펄스폭이다. Nsf는 서브필드의 개수를 나타낸다. 펄스의 폭과 1TV-field의 시간은 모두 10<sup>-6</sup>초[μs]로 통일 시켜 주었다. 본 연구의 결과로 제시된 어드레스 및 표시방전 유지펄스의 최소 펄스폭을 식 (3)에 적용하여 각 SF의 개수에 따른 표시방전 유지펄스의 개수를 비교하면 다음과 같다.

$$\frac{16600 [\mu\text{s}]}{Tsus [\mu\text{s}]} - (Treset [\mu\text{s}] + Nscan * Tad [\mu\text{s}]) Nsf \quad \text{개} \quad \dots \quad (3)$$

| 어드레스 펄스폭   | sub-field 개수 | 표시방전 유지펄스의 개수<br>(표시방전 유지펄스폭 : $2\mu s$ ) |

|------------|--------------|-------------------------------------------|

| $1.5\mu s$ | 8            | 3292 개                                    |

|            | 9            | 2666 개                                    |

|            | 10           | 2040 개                                    |

|            | 11           | 1414 개                                    |

|            | 12           | 788 개                                     |

(a) 주사선수 768개의 경우

| 어드레스 펄스폭   | sub-field 개수 | 표시방전 유지펄스의 개수<br>(표시방전 유지펄스폭 : $2\mu s$ ) |

|------------|--------------|-------------------------------------------|

| $1.5\mu s$ | 8            | 1420 개                                    |

|            | 9            | 560 개                                     |

|            | 10           | -300 개                                    |

(b) 주사선수 1080개인 경우

표 1. 어드레스 펄스폭과 sub-field의 개수에 따른 표시방전 유지펄스의 수

Table.1. The number of sustain pulse according to the number of the sub-field and the address pulse width.

최소펄스 폭 조건인 어드레스 펄스폭  $1.5\mu s$ , 표시방전 유지펄스 폭  $2\mu s$ 인 경우 수평 주사선수 768개에서 Sub-field를 최대 11개 까지 구동시킬 수 있으며 수평 주사선수가 1080개에서는 Sub-field의 개수를 최대 8개까지 구동시킬 수 있다. 각 경우의 최대 Sub-field의 개수는 본 연구의 실험 결과에서 1024개의 표시방전 시 얻어진 휘도값인  $310[\text{cd}/\text{m}^2]$  이상을 가지는 조건이다. 위의 결과로 각 수평주사선수에 따른 최대 Sub-field 구동 시 이론적으로 약  $430[\text{cd}/\text{m}^2]$ 의 휘도를 얻을 수 있다. 따라서 1080개와 768개의 수평 주사선수에 따라 각각 8개와 11개의 Sub-field를 가지는 PDP 구동이 가능하다.

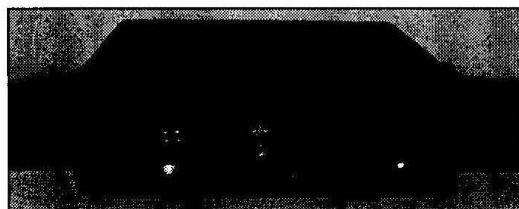

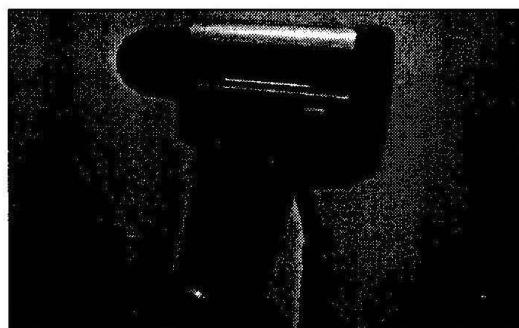

### 3. 구현된 화상

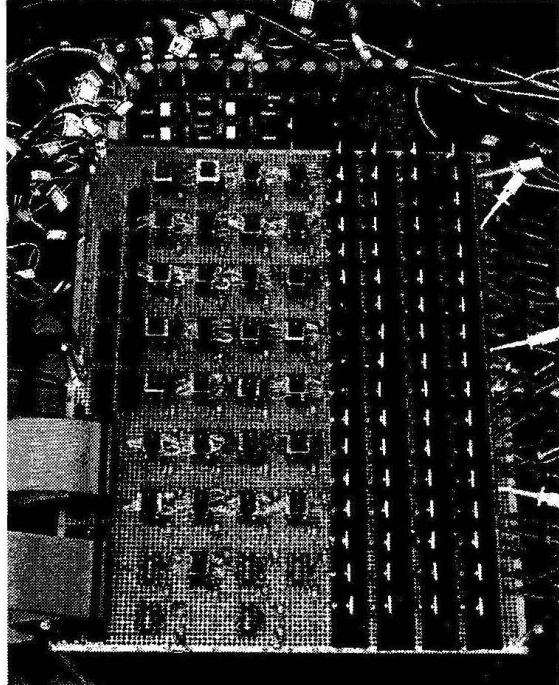

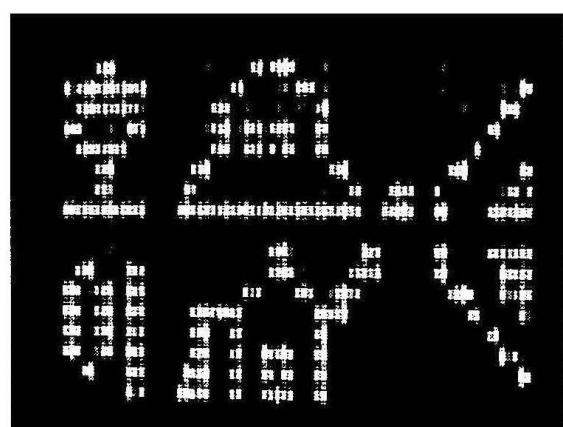

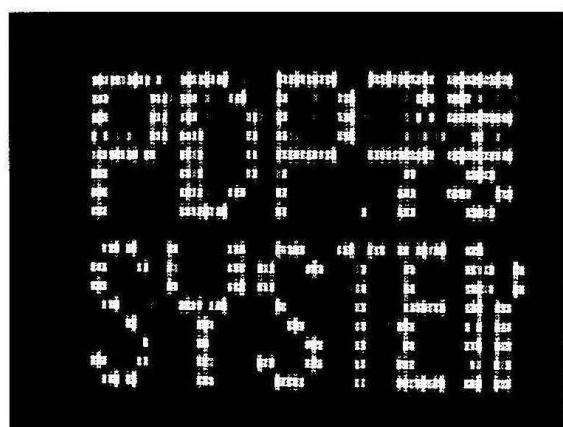

다음은 본 연구의 결과로써 PDP에 구현된 화상이다. 그림 27은 8bit의 sub-field 구조를 갖는 ADS 구동법에 의해 패널상에 16단계의 계조를 표현한 것이다. 그림 28은  $75 * 16$  pixel로 구성된 면적을 30개의 Data 드라

이 버와 16개의 scan 드라이버로서 구동시킨 화면이다.

그림 27. 16계조 구현

Fig. 27. The realization of 16 gray scale

그림 28. 화상 구현

Fig. 28. The realization of the image

## V. 결론

본 연구에서는 PDP 구동 실험장치를 개발하였으며 개발된 실험장치를 이용하여 3전극 면방전 AC PDP에 현재 가장 널리 사용되는 상용의 ADS 구동방식을 적용하여 다음과 같은 결론을 도출하였다.

첫째, 개발된 PDP 구동 실험장치의 주요 특징을 요약하면 다음과 같다.

- ① 구동에 필요한 로직 펄스를 디지털시스템 설계 프로그램을 사용하여 짧은 시간 내에 설계할 수 있으며 컴퓨터로 시뮬레이션하여 검증할 수 있으므로 신뢰도가 높다.

- ② PDP의 구동 타이밍의 기본이 되는 로직블록을 설계하였다. 이 로직블록들은 다수의 2진 스위치를 가지며 프로그램 상에서 이 스위치들을 ON/OFF 하는 것만으로 PDP 구동에 필요한 각종 펄스를 손쉽게 설계 할 수 있다 또한 펄스타이밍의 수정도 손쉽게 할 수 있다.

- ③ PDP의 구동을 위해서는 백 수십 V(Voltage)의 고전압펄스를 짧은 시간 내에 수많은 셀들에 공급해주어야 한다. 본 논문에서 개발된 PDP 구동실험장치는 최대 2MHz 까지 고속구동펄스를 발생 시킬 수 있다.

둘째, 3전극 면방전 PDP에 8bit 256계조를 표현할 수 있는 ADS 구동법 을 구현하였으며 이를 이용하여 소면적의 패널면에 16계조의 표현과 정지 화상 및 동화상을 나타내었다.

셋째, 최소의 어드레스와 표시방전 유지펄스폭으로 휙도의 저감이 없는 안정적인 표시방전유지의 조건을 실험적으로 아래와 같이 도출하였다.

어드레스 펄스의 폭이  $1.5\mu s$  이상만 되면 표시 방전을 위한 벽전하 축적에 문제가 없으며 이때의 동작전압은 100V - 135V 사이로 35V의 마진을 갖는다. 한편 표시방전 유지펄스의 폭은  $2\mu s$  이상 되어야 하며 이때의 방전 안정 최대 전압은  $2\mu s$  이상에서 대략 190V로 25V의 마진을 갖는다. 이 결과를 이용하면 최대 수평 주사선수가 1080라인 이면서 8개의 sub-field를 가지는 PDP 구동시 표시방전 유지펄스의 개수를 1420개 까지 사용할 수 있다.

본 연구에서 개발된 구동장치는 PLD에 비해 구동회로에 사용된 FET의 동작속도가 느리다. 따라서 향후 초고속 스위칭이 가능한 고전압 소자들이 개발된다면 지금보다 더 빠른 펄스의 구현도 가능할 것으로 보여 지며, 또한 패널특성을 향상시켜 어드레스 펄스폭을 더욱 좁게 가져갈 수 있다면 표시방전 유지펄스의 개수를 더욱 증가시켜 더 높은 휘도를 얻을 수 있을 것으로 사료된다.

## [ 참고문헌 ]

- [1] Tadatsugu Hirose, Kyoji Kariya, "Present Status and Future Prospect of Technological Development on Color PDPs", IDW'99, pp.11-14, 1999

- [2] T. Kishi. et al., "A New Driving Technology for PDPs with Cost Effective Sustain Circuit", SID Digest of Tech. Papers, pp.1236-1239, 2001

- [3] 松本正一 編著, 姜元浩 외 共譯, "Electronic Display", 성안당, pp.83-117, 1998

- [4] T. Shinoda, et, al. "Improvement of Luminance and Luminous Efficiency of Surface-Discharge Color ac PDP", SID91 DIGEST, pp.724-727, 1991

- [5] T. Shinoda, "Plasma display Panels", Optoelectronics Devices and Technologies, Vol.7, No.2, pp231-251, 1992

- [6] S. kanggu, et. al., "A 31-in-Diagonal Full-Color Surface-Discharge ac Plasma Display Panel", Digest of SID'92, pp.713-716, 1992

- [7] 田春生, “放電・高電圧工學”, 東明社, 1993

- [8] 염정덕, “플라즈마 디스플레이의 공간전하 특성에 관한 연구”, 조명·전기설비학회논문지, Vol.15, No.6, pp.1-7, 2001.11

- [9] 박수효 외, “텔레비전 방송시스템”, 복두출판사, 1999

- [10] K. Yoshikawa, et. al., "A Full Color AC Plasma Display with 256 Gray Scale", JAPAN DISPLAY'92, pp.605-608, 1992

- [11] 염정덕, “HDTV급 플라즈마 디스플레이의 고속 어드레스 방전특성에 관한 연구”, 조명·전기설비학회논문지, Vol.15, No.1, pp.13-21, 2001.1

- [12] 황기웅 외, “디스플레이공학 II”, 청범출판사, 2000

- [13] 염정덕, “PDP의 ADS 구동방식에서의 초기화 방전특성에 관한 연구”, 조명·전기설비학회논문지, Vol.17, No.2, pp.17-22, 2003.3

## [ 연구실적 ]

### < 국내 학술지 논문게제 >

- [1] 손현성, 임찬호, 염정덕, "PLD를 사용한 PDP용 구동실험장치의 개발", 조명 · 전기설비학회논문지, Vol. 18. No 3. pp.48-54, 2004.5.31

### < 국내 학술대회 논문발표 >

- [1] 염정덕, 채승엽, 손현성, "플라즈마 디스플레이 패널의 방전 AND gate에 관한 연구", 조명 · 전기설비학회 학술대회논문집, pp.39-44, 2001.11.1

- [2] 손현성, 채승엽, 염정덕, "PDP의 프라이밍 방전특성에 관한 연구", 조명 · 전기설비학회 학술대회논문집, pp.29-33, 2002.11.6

- [3] 손현성, 이재희, 염적덕, "PDP의 AC Floating 방전특성에 관한 연구", 조명 · 전기설비학회 학술대회논문집, pp.49-53, 2003.11.7

- [4] 이재희, 손현성, 염정덕, "PDP의 DC Floating 방전셀 상호간 영향에 관한 연구", 조명 · 전기설비학회 학술대회논문집, pp.55-59, 2003.11.7

- [5] 염정덕, 손현성, "방전 AND Gate PDP의 특성 개선에 관한 연구", 조명 · 전기설비학회 춘계학술대회논문집, pp.24-28, 2004.5.8

- [6] 손현성, 염정덕, "방전 AND Gate PDP의 공간전하 의존성에 관한 연구", 조명 · 전기설비학회 춘계학술대회논문집, pp.248-252, 2004.5.8

- [7] 손현성, 염정덕, "구동펄스 인가조건에 따른 PDP의 휴드 특성에 관한 연구", 조명 · 전기설비학회 추계학술대회논문집, pp.57-62, 2004.11.3

### < 수상실적 >

- [1] 2004년도 추계 학술대회 우수 논문상, 한국 조명 · 전기설비학회, 2004. 11. 3

# A study on the characteristics of AC driving method for 3 electrodes surface discharge AC PDP

Son, Hyun sung

Department of Computer and Electronic Engineering

The Graduate School, Gyeongju University

(Supervised by Professor Ryeom, Jeong duk)

## (Abstract)

This paper present the experimental PDP driving system which allow us the PDP driving experiment more easily. The system will enable us to design and simulate the PDP driving pulses and show the resulting response of the PDP. Based on the designed timing waveform, we can program the PLDs which ultimately control the high voltage FET switches. Compared to the previous PDP driving system using the logic gate ICs, the system we developed not only reduces the design time but also make the modification more easy.

Using the developed driving system, we analyzed the result of the interaction between the address discharge and sustain discharge based on the PDP driving pulse condition change. The PDP driving pulse followed the ADS driving method for the commercialized three electrodes AC PDP. As a result of the experiment, a minimum address pulse width for the address discharge turned out to be  $1.5\mu s$  and the operation margin of the

address voltage is 35V. A minimum sustain discharge pulse width for address discharge is  $2\mu s$  and the operation margin of sustain voltage is 25V. The voltage of sustain discharge for a maximum brightness is 190V at this time, and the average brightness is 310[cd/m<sup>2</sup>] when the number of a sustain discharge pulse is 1024.